Het ontwerp van elektronische PRODUCTen gaat van het tekenen van schematische diagrammen tot de PCB-indeling en bedrading. Door een gebrek aan kennis op dit gebied van werkervaring komen er vaak verschillende fouten voor, waardoor ons vervolgwerk wordt belemmerd en in ernstige gevAlleen kunnen de gemaakte printplaten helemaal niet worden gebruikt. Daarom moeten we ons best doen om onze kennis op dit gebied te verbeteren en Alleerlei soorten fouten te vermijden.

Dit artikel introduceert de veel voorkomende boorproblemen bij het gebruik van PCB-tekentafels, om te voorkomen dat u in de toekomst op dezelfde putten stapt. Boren is onderverdeeld in drie categorieën: door het gat, het blinde gat en het ondergrondse gat. Doorlopende gaten omvatten plug-in gaten (PTH), schroefpositioneringsgaten (NPTH), blinde, ondergrondse gaten en via gaten (VIA) door gaten, die Alleemaal de rol spelen van meerlaagse elektrische geleiding. Ongeacht het type gat is het gevolg van het probleem van ontbrekende gaten dat niet de gehele partij PRODUCTen direct kan worden gebruikt. Daarom is de juistheid van het boorontwerp bijzonder belangrijk.

Casusuitleg van putten en lekken aan de ontwerpkant van printplaten

Probleem 1: De door Altium ontworpen bestandsslots zijn misplaatst;

Beschrijving van het probleem: De sleuf ontbreekt en het PRODUCT kan niet worden gebruikt.

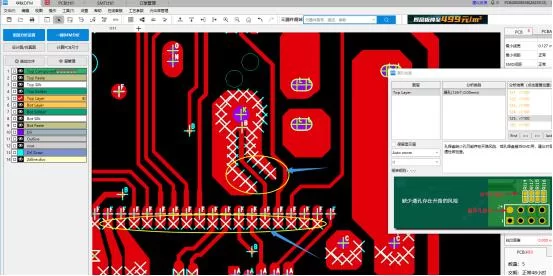

Reden analyse: De ontwerpingenieur heeft bij het maken van de verpakking de sleuf voor het USB-apparaat gemist. Toen hij dit probleem ontdekte bij het tekenen van het bord, wijzigde hij het pakket niet, maar tekende hij rechtstreeks het slot op de gatensymboollaag. In theorie is er geen groot probleem met deze handeling, maar tijdens het PRODUCTieproces wordt Alleeen de boorlaag gebruikt voor het boren, dus het is gemakkelijk om de aanwezigheid van sleuven in andere lagen te negeren, wat resulteert in het gemist boren van deze sleuf en het PRODUCT kan niet worden gebruikt. Zie onderstaande afbeelding;

Hoe kuilen te vermijden: Elke laag van het OEM PCB-ontwerpbestand heeft de functie van elke laag. Boorgaten en sleufgaten moeten in de boorlaag worden geplaatst en er kan niet van worden uitgegaan dat het ontwerp kan worden vervaardigd.

Vraag 2: Door Altium ontworpen bestand via hole 0 D-code;

Beschrijving van het probleem: De lekkage is open en niet-geleidend.

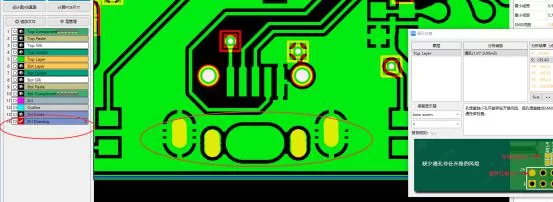

Oorzaakanalyse: Zie figuur 1. Er zit een lek in het ontwerpbestand en het lek wordt aangegeven tijdens de DFM-maakbaarheidscontrole. Nadat de oorzaak van het lek is gecontroleerd, is de diameter van het gat in de Altium-software 0, wat resulteert in geen gaten in het ontwerpbestand, zie Figuur 2.

De reden voor dit lekgat is dat de constructeur een fout heeft gemaakt bij het boren van het gat. Als het probleem van dit lekgat niet wordt gecontroleerd, is het moeilijk om het lekgat in het ontwerpbestand te vinden. Het lekgat heeft rechtstreeks invloed op de elektrische storing en het ontworpen PRODUCT kan niet worden gebruikt.

Hoe kuilen te vermijden: Testen op de maakbaarheid van DFM moeten worden uitgevoerd nadat het ontwerp van het schakelschema is voltooid. De gelekte via's kunnen tijdens het ontwerp niet worden gevonden tijdens de PRODUCTie en PRODUCTie. Testen van de maakbaarheid van DFM vóór PRODUCTie kunnen dit probleem voorkomen.

Figuur 1: Ontwerpbestandslek

Figuur 2: Altium-diafragma is 0

Vraag 3: De door PADS ontworpen bestandsvia's kunnen niet worden uitgevoerd;

Beschrijving van het probleem: De lekkage is open en niet-geleidend.

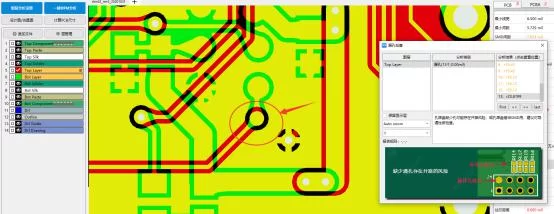

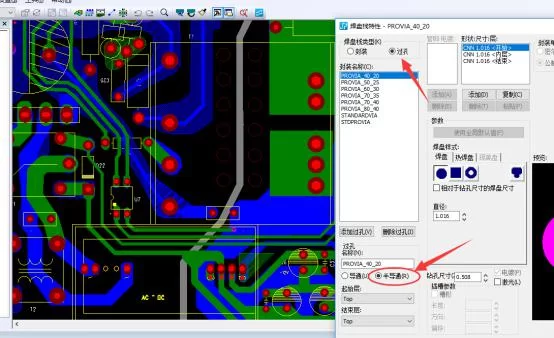

Oorzaak Analyse: Zie figuur 1. Bij gebruik van DFM-fabricagetests wijst dit op veel lekken. Na onderzoek naar de oorzaak van het lekkageprobleem werd een van de via’s in PADS ontworpen als een halfgeleidend gat, waardoor het ontwerpbestand het halfgeleidende gat niet weergaf, wat resulteerde in een lek, zie Figuur 2.

Dubbelzijdige panelen hebben geen halfgeleidende gaten. Ingenieurs hebben tijdens het ontwerp gaten via gaten ten onrechte als halfgeleidende gaten aangemerkt, en halfgeleidende gaten bij de uitvoer lekken tijdens het boren, wat resulteert in lekkende gaten.

Hoe kuilen te vermijden: Dit soort verkeerde handelingen zijn niet gemakkelijk te vinden. Nadat het ontwerp is voltooid, is het noodzakelijk om analyses en inspecties van de maakbaarheid van DFM uit te voeren en problemen op te sporen vóór de PRODUCTie om lekkageproblemen te voorkomen.

Figuur 1: Ontwerpbestandslek

Afbeelding 2: PADS-software via's met dubbel paneel zijn halfgeleidende via's